|

|||||||||||||||||||||

| Top > Macintosh > iMac > inside of the iMac G5 ▼NAV ▼form ←Previous | |||||||||||||||||||||

321_ iMac G5 17 inch model and 20 inch model

|

|||||||||||||||||||||

322_ Architecture block diagram and Bus speedDeveloper Noteが公開され、詳細が徐々にわかってきた。目新し いユニットとしてShasta I/O Controllerがある。長い間Keylargo ICがその役目をしてきたが、G5になりMemory ControllerをIBMがあわせて生産するようになると、どうしてもApple独自のデバイスコントローラーチップが必要になる。 |

PowerMac G5 1.8GHz single CPUにGeForce FX 5200 Ultraを組み合わせたシステムと比較した場合、ダウングレードされた場所はプロセッサーインターフェースが3.6GB/s×2から2.4GB/s×2へ、I/O ControllerへのHyper Transportが1.6GB/s×2から800MB/s×2へ半減していることだ。 これらがボトルネックになり得るのか。一部公開されたベンチマークと手ものとのPowerMac G5の値を比較した。 |

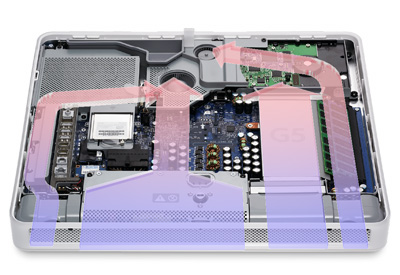

323_ the cooling sysytem of the iMac G5長い間、電源コントロールおよびキーボードインターフェースを司ってきたPMU 99はSystem Management Unit(SMU)に置き換わった。 温度センサーによる情報だけでなく、消費電力も監視し、3つのブロワーを細かく制御し、動作音を最低限に保つ役目をしている。 外側からは吸気口と排気口はそれぞれ一つに見えるが、内部では吸排気の経路が巧みに分割され、それぞれ独立した制御が行われている。 画像はApple社の使用許諾に準拠して使用しています。 |

323_ the cooling system of the iMac G5 |

iMacの内部写真は公開直後からApple社のWebページに掲載されていました。今回は公開されたDeveloper Noteとあわせて、iMac G5の内部構造について考えていきたいと思います。iMac G5はスクリーン一体型で厚みが約5cmと大変薄くなっています。323_ the cooling sysytem of the iMac G5に廃熱経路の予想図を示しました。iMacではPMU 99に替わり、SMUが基板温度センサーだけではなく、消費電力もあわせてモニターし、ブロアー回転速度を制御しています。SMUはOSによって制御され、OSがハングアップしたり、制御信号をサポートしなければ、2分で最大出力になるよう安全装置が組み込まれています。320_ inside of the iMac G5でわかるように、基板中央の広い面積を占めているのは定電圧回路です。PowerBookに搭載するには、まだ大きすぎますが構成するチップの省電は着実に進んでいる様子です。Developer NoteによるとU3L(Uni-North 3 Lite)と呼ばれる新しいMemory |

Controllerは90nmとSOIを組あわせた最新のプロセスルールで製造されています。Liteとされていますが、アドレッシングはU3と同様42bitをサポートし、Processor BusとI/O Controller用のHyperTransportのコンフィグレーションが遅く設定されていることを除けば、シングルCPUのMemory conrollerとしての条件はすべて備えています。では、どの程度の性能低下があるのでしょうか。G4と比較しG5はスループットを重視します。小さなメモリアクセスのレイテンシは1.5倍に悪化し、キャッシュラインの増大はソフトウェアの設計によっては3倍のオーバーヘッドを生じ、あっという間にバスを飽和させてしまいます。例えばCPU内部のキャッシュを抑制した場合、バス性能だけ比較すればG5はG4の4分の1程度の性能しか出ません。G5はメモリアクセスに関しては、4本の先読み回路を持ち、バスを最大限に活用します。そういう意味でも、G5のProcessor Busには方向性があって、 |

上りと下りの帯域が制限されています。双方向Busの場合、切り換え制御のオーバーヘッドが生じますが、帯域分配の自由度はあがります。G5の特性を考えると前者が適しているのでしょう。128bitの連続したLoad命令を内部キャッシュが飽和するまで発行した場合(現実には起こりえない)の速度を調べると、PowerPC 970 1.8GHz/ Processor Bus 900MHzで約3GByte/secという値が得られました。G4の740MByte/secと比較すると4倍です。実機がない現在、同じテストをiMacで調査することは無理ですが、iMac G5の理論上のバス速度である2.4GByte/secを超えています。それではどの程度の影響があるのでしょうか。現在入手できるベンチマークテスト結果(Xbench)を、もっとも類似する構成のPowerMac G5と比較したのが322_ Architecture block diagram and Bus speedです。Processor Busを経由しメモリ、AGP、HyperTransportのそれぞれについて比較した値を示しました。メモリ、AGPに関してはPowerMac G5の96%の性能を発揮しており、Processor Busが大きなボトルネックになっていない |

ことを示しています。しかし、Serial ATAドライブへの連続書き込みテストの性能が約半分にとどまっています。半分の速度に押さえられたHyperTransportが影響しているのでしょうか。同時に行われた連続読み込みテストではPowerMac G5と同程度の値を示していることからHyperTransportの影響はわずかであると考えられます。それならどこが原因なのでしょうか。iMac G5のキーデバイスの一つとしてShesta I/O Controllerがあります。medical macintoshではI/O Controllerについて、1998年にHeathrowを2つ搭載したPowerBook G3 seriesから追いかけています。短命だったPaddingtonを経て、1999年7月にiBookの発表とともにKeylargo I/O Controllerがリリースされました。何度かの小変更を受け、一時はPangeaやIntrepidに統合されながら、PowerMac G5でHyperTransportに対応し、Serial ATAやFireWire Link Layer、PCI BridgeをもつKeylargo 2へ進化しました。それではShesta I/O Controllerはどのような位置づけ |

になるのでしょうか。Keylargo 2と比較すると、USB 1.0が削除されるなど簡略化が進む一方、ATA/133の搭載など強化部分もあります。ATA/133に関しては、教育機関向けiMac G5の40GByteのATAドライブ搭載用とされていますが、今後のPowerBook G5の布石とも受け取れます。さて、Serial ATAドライブへの連続書き込みテストが振るわなかったのはなぜでしょうか。ドライブベンチマークテストは同じテスト環境を用意することが大変難しいテストでもあります。今回のテスト環境に問題があったと説明しても良いでしょう。しかし、新しいShesta I/O Controllerに問題が隠れているとしてもおかしくありません。とくにデバイス内部のキャッシュポリシーの設定によっては、スループットが半分程度に落ちることはこれまでも観測されてきました。Shesta I/O Controllerの熟成が進めば、こうした問題はすぐにクリアされるでしょう。それまでは、ボトルネックの無いこと |

が確認されたU3 Lite周りの強化、とくに大量のディスクアクセスを抑制するために、メモリは多めに積んでおくことがiMac G5の本来の性能を発揮するために必要なことであると感じました。 |

- Architecture

- iBook

- iBook Dual USB

- iBook 16VRAM

- PowerMac G4

- PowerMac G4 Dual

- PowerMac G4 Mirrored drive doors

- PowerMac G5

- iMac

- iMac flat panel

- iMac G5

- iMac G5について

- iMac G5の内部構造とShasta I/O Controllerについて

- Lombard

- PISMO

- PowerBook G4 Titanium

- PowerBook G4 Gigabit Ethernet

- PowerBook G4 DVI

- PowerBook G4 DVIについて(Architecture Block Diagram)

- PowerBook G4 1GHz/867MHz

- Gigahertz PowerBook (PowerBook G4のアーキテクチャの変遷)

- PowerBook G4 17-inch

- PowerBook G4 12-inch

- PowerBook G4 15-inch FW800

- Xserve

- PowerPC

- Macintosh

medical macintosh (c) 1998,1999,2000,2001,2002,2003,2004,2005, 2006

Written/Edited by Y.Yamamoto M.D.

Privacy and Security Policy

ご自由にリンクして下さい。アップルおよびアップルのロゴは、アメリカ合衆国およびその他の国々におけるApple Computer,Inc.の登録商標です。POWERBOOK ARMYおよびmedical macintoshは、独立したユーザグループで、アップルコンピュータ株式会社が権限を与えた団体、支援する団体、またはその他に承認する団体ではありません。 |